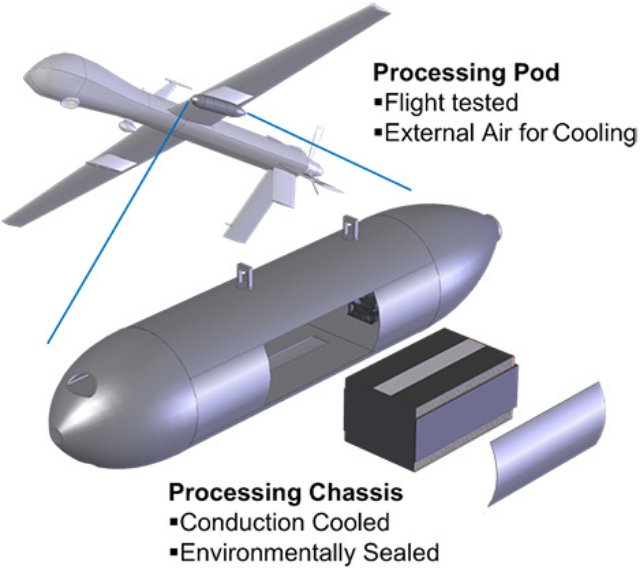

SRC has been focused on solving myriad problems that exist around the data analysis requirements of intelligence, surveillance and reconnaissance (ISR) missions. In an effort to bring big data analysis closer to the sensor, SRC has developed Agile Condor for the US Air Force Research Lab (AFRL) in Rome, NY. The Agile Condor pod system is a scalable, low cost, size, weight and power (low-CSWaP) hardware architecture that enables high-performance embedded computing (HPEC) on-board remotely piloted aircraft (RPA).

The Agile Condor flight-configured pod system consists of an external pod enclosure and an internal chassis that supports the use of commercial off-the-shelf (COTS) single-board computers (SBCs), graphics processing units (GPUs), Field-Programmable Gate Arrays (FPGAs), and solid-state storage devices (SSDs). The pod enclosure is based on an existing, flight-certified design specifically modified to use ambient air cooling for thermal management of the embedded electronics. The chassis utilizes a modular, distributed network of processors and co-processors based on open industry standards to deliver more than 7.5 teraflops of computational power at better than 15 gigaflops per watt. The COTS upgradeable architecture of the Agile Condor system provides for fast technology refresh, which decreases life cycle costs, reduces system downtime, and assures continued usefulness of the system. Read more

Source: www.uasvision.com